## Hysteresis characteristics of hetero-structured devices using two-dimensional materials for memory applications

**Min Sup Choi<sup>1</sup>**, Gwan-Hyoung Lee<sup>2</sup>, Young-Jun Yu<sup>2,3</sup>, Dae-Yeong Lee<sup>1</sup>, Seung Hwan Lee<sup>1</sup>, Philip Kim<sup>2</sup>, James Hone<sup>2</sup>, and Won Jong Yoo<sup>1</sup>

<sup>1</sup>SKKU Advanced Institute of Nano-Technology (SAINT), Sungkyunkwan University, 2066 Seobu-ro, Jangan-gu, Suwon, Korea

<sup>2</sup>Columbia University, 10027 New York, USA

<sup>3</sup>Electronics and Telecommunications Research Institute (ETRI), 218 Gajeong-ro, Yuseong-gu, Daejeon, Korea

goodcms@skku.edu

## Abstract

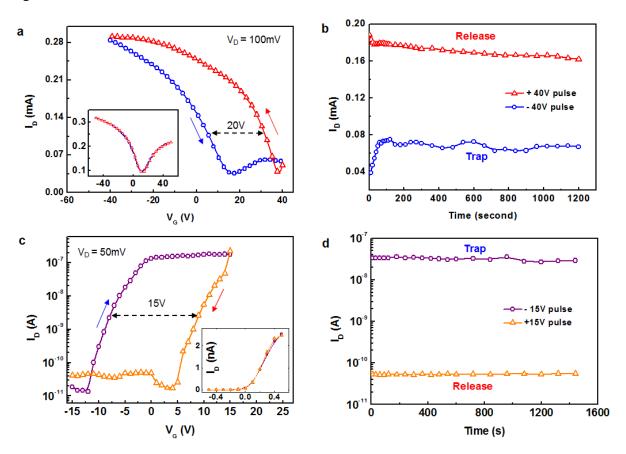

Recently, various hetero-structured devices using two-dimensional materials have been developed due to its high performances and flexibility.<sup>[1]+[3]</sup> In this work, the ultrathin memory devices consisting of two-dimensional (2D) materials were fabricated by stacking graphene, hexagonal boron nitride (hBN), and molybdenum disulfide (MoS<sub>2</sub>), demonstrating large memory window and good retention properties as shown in Figure 1. The two different device structures of, graphene/hBN/MoS<sub>2</sub> (GBM) and MoS<sub>2</sub>/hBN/graphene (MBG), where graphene and MoS<sub>2</sub> were employed as channel and charge trap layer for GBM and vice versa for MBG, were investigated. Even though both device structures exhibit a large hysteresis, their field effect transistor (FET) characteristics are quite different. The large hysteresis for memory application can be induced by quantum tunneling effect through the thin hBN layer (< 10 nm) and charge trapping in underlying 2D layer.<sup>[1],[4]</sup> By formation of the potential wells in the underlying MoS<sub>2</sub> or graphene layers between SiO<sub>2</sub> and hBN dielectrics, the charges can tunnel through ultrathin hBN layer and be effectively trapped or released depending on the applied gate voltages. We observed that these trapped charge can be maintained in potential wells and this induces the significant hysteresis in the current - voltage transfer curves of the 2D FETs. These results provide a promising way to fabricate memory devices using 2D materials.

## References

- [1] Britnell, L. et al., Science, 335 (2012) 947-950.

- [2] Georgiou, T. et al. Nat. Nanotech., 8 (2013) 100-103.

- [3] Yu, W. J. et al. Nat. Materials, (2012) doi: 10.1038/nmat3518.

- [4] Lee, G. –H. et al. Appl. Phys. Lett., 99, (2011) 243114.

Figures

**Figure 1.** (a) Transfer curve ( $I_D$ - $V_G$ ) and (b) Retention performance of the GBM device with hBN of 6 nm and  $MoS_2$  of 5 nm. The inset of (a) shows a transfer curve of GB (Graphene/hBN). (c) Transfer curve and (d) Retention performance of the MBG device with hBN of 12 nm,  $MoS_2$  of 3 layers, and graphene of 2 layers. The inset of (c) shows a transfer curve of the same device when graphene was used for gating.